内存时序是什么?对性能影响有多大?内存入门级知识科普来了

说起内存参数,大家肯定多知道容量、频率,甚至是电压、颗粒来源等,但和频率一样决定了内存性能高低的时序(也常说延迟),却往往容易被忽视。

今天,影驰就内存时序做了一个简单的科普,一起来了解下。

内存频率是一个数字,而内存时序则是一大串数字,最常用的就有4个,表述的时候中间用破折号隔开,例如16-18-18-38。

这些数字都表示延迟,也就是内存的反应时间。当内存接收到CPU发来的指令后,通常需要几个时钟周期来处理它,比如访问某一块数据,这就对应时序参数。

当然了,这个处理时间越短,内存性能越好。

内存时序4个数字对应的参数分别为CL、tRCD、tRP、tRAS,单位都是时间周期,也就是一个没有单位的纯数字。

CL(CAS Latency):列地址访问的延迟时间,是时序中最重要的参数

tRCD(RAS to CAS Delay):内存行地址传输到列地址的延迟时间

tRP(RAS Precharge Time):内存行地址选通脉冲预充电时间

tRAS(RAS Active Time):行地址激活的时间

看完感觉更懵圈了?没关系,给你举个例子。

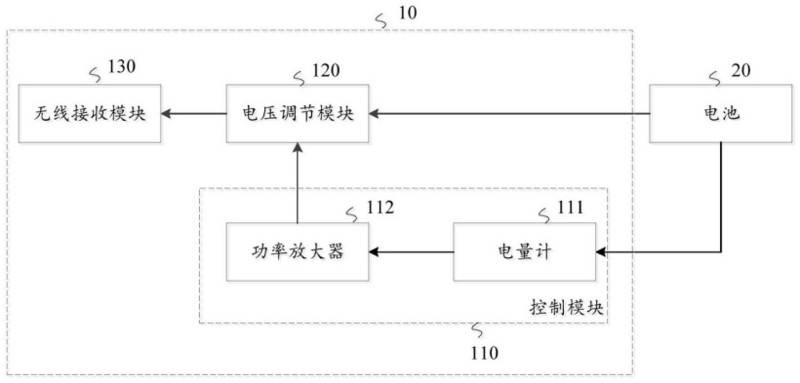

我们可以把内存存储数据的地方想象成下面这样,每个方格都存储着不同的数据。CPU需要什么数据,就向内存发来相应的指令,比如想要的位置是C4。

内存收到CPU的指令之后,要先确定数据具体在哪一行,时序的第二个参数tRCD就代表这个时间,意思就是内存控制器接收到行的指令后,需要等待多长时间才能访问这一行。

由于每一行都有多个数据,内存并不能哪一个才是CPU需要找的,所以tRCD只是一个估值,这也就是为什么小幅改动这个数值,并不会显著改变内存的性能。

内存确定了数据所在的行之后,要想找出数据,还得确定列。时序的第一个数字也就是CL(CAS),就表示内存确定了行数之后,还得等待多长时间,才能访问具体的列数(时间周期)。

行列必然产生交点,也就是说确定了行数和列数之后,就能准确找到目标数据,所以CL是一个准确的值,任何改动都会影响目标数据的位置,所以它在时序当中是最关键的一个参数,对内存性能的发挥着举足轻重的作用。

内存时序的第三个参数tRP,就是如果我们已经确定了一行,还要再确定另外一行所需要等待的时间(时间周期)。

第四个参数tRAS,可以简单理解成内存写入或者读取数据的一个时间,它一般接近于前三个参数的总和。

所以,在保障稳定性的前提下,内存时序越低越好,而高频率和低时序是个矛盾体,一般频率上去了,时序就得有所牺牲,要想足够低的时序,频率又很难拔高。

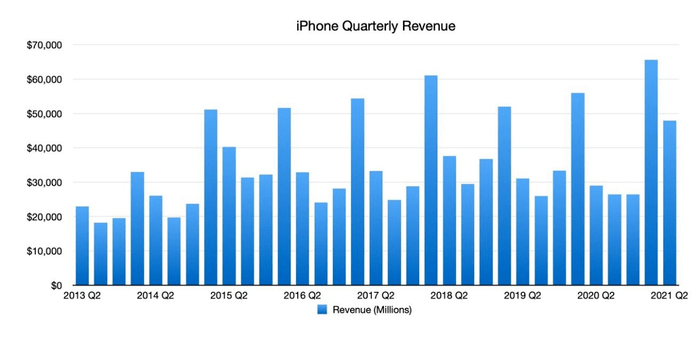

那么,时序对内存性能的影响到底有多大呢?

我们做了一个测试,保持内存频率不变,可以看到,内存的性能随着时序的变小而不断变强。

另外,时序改变后,内存延迟的变化比内存读写速度的变化更加明显,这也说明时序对内存的影响,更侧重在延迟方面。

现在,你懂了吗?

新闻 2021-05-11 08:35:29

新闻 2021-05-11 08:35:29

营业执照公示信息

营业执照公示信息

相关新闻